This article refers to the address: http://

Abstract: IME6400 is an integrated circuit chip developed by INTIME of Korea to support MPEG4 high-resolution real-time video coding. This paper introduces the performance characteristics of the IEM6400 chip, and gives a specific method for designing a digital video surveillance system based on the embedded PC core.Keywords: MPEG4; IME6400; embedded system; encoder

1 Overview

MPEG4 is a member of the Moving Picture Expert Group standard series and is a solution developed by the International Organization for Standardization for multimedia communications. The main feature of MPEG4 is the encoding of the content in the image. It has more advantages than MPEG2 encoding. To this end, South Korea's INTiME Corporation introduced the integrated circuit chip IME6400 that supports the MPEG4 standard encoding scheme, which led to the study of the use of the integrated circuit to improve the speed and performance of the monitoring system. This paper introduces the chip in combination with the application of IME6400 in embedded system.

2 IME6400 performance characteristics

The IME6400 is a multi-channel digital audio and video coding system-on-a-chip in a 240-pin PQFP package that supports MPEG4/2/1 video compression coding standards and supports I, P, and B frame compression. The image size can be programmed to a maximum size of 2048×2048; the code rate can support fixed and variable rate compression, and supports dynamic detection.

The IME6400 supports 48/44.1/32/ 24/ 22.05/ 16kHz audio sampling. Its synchronous serial interface is an optional external audio DSP. The external interface uses 32-Bit to synchronize the DRAM bus interface with the external HOST interface of 8/16Bit. In addition, the IME6400 requires an external 27MHz clock.

3 IME6400 main pin function

3.1 SDRAM pin

The SDRAM interface in the IME6400 supports a 32-bit synchronous DRAM bus interface. Different sizes of SDRAM from 4Mbits to 64Mbits can be selected according to different needs. When high resolution, MPEG4 encoding is required, the minimum SDRAM size should be 32 Mbits. The main pin functions of the SDRAM interface are as follows:

DD[31:0]: SDRAM data bus.

DA[14:0]: SDRAM address bus, where DA[14:13] is connected to BANK[1:0] of SDRAM.

DNWE: SDRAM write enable signal, low effective.

DNCS: SDRAM chip select signal, low effective.

DQM: The input/output mask of the SDRAM data is enabled.

NRAS: SDRAM row address strobe, low effective.

NCAS: SDRAM column address strobe, low active.

CKE: Clock enable signal, high active.

CKO: External SDRAM clock output. When reading and writing data from SDRAM, it should be sampled from its rising edge.

3.2 Video Signal Pin

The IME6400 chip encodes digital video signals from the CCIR-601 interface. For analog video signals from a camera or playback device, A/D sampling is required first to turn it into the desired signal format. The function of the video signal interface pin is described as follows:

VD[15:0]: Digital YUV signal input.

VSYNC: Vertical sync signal, its active polarity is programmable, the default is high active.

HSYNC: Horizontal sync signal, active high.

DVALID: The effective indicator of the video signal. When it is low, it means that the video data is invalid; and when it is high, it means that the input video data is valid.

PCLK: Point clock input, the input video data is sampled on the rising edge of the clock. This clock should be provided by an external video A/D chip. Because the IME6400 only supports 16bits video interfaces, a 13.5MHz clock frequency should be provided.

FIELD: Parity indicator.

3.3 Static Memory Pins

Since the IME6400 is based on a CPU core, the power-on initialization must be initiated from the ROM. There are two ways to start the IME6400, one is through the internal ROM, and the other is through the static memory interface external ROM to boot. It is recommended to use an external ROM to boot the IME6400. The pin functions of this interface are as follows:

ADR[16:0]: Static memory address bus.

DATA[7:0]: Static memory data bus.

NRST: Master chip reset signal, active low.

MCLK: main chip clock input terminal, different frequencies correspond to different resolutions. When it is connected to high resolution, it should be connected to 27MHz clock. At this time, the image size can be 640×480, 720×480, 768×576, etc., frame rate. It is 25 to 30 frames/second.

RADR[1:0]: ROM low address signal.

RNOE: ROM data output enable signal terminal, low effective.

EXTBOOT: When the termination is low, the chip boots from the internal ROM; when it is high, the chip boots from the external ROM.

SNOE: SRAM data output enable signal, low active.

SNWE: SRAN data write enable signal, low active.

GPIO[7:0]: Programmable pin.

3.4 I2C Interface Pins

The IME6400 can be used as the master of the I2C to configure the internal registers of the video A/D chip to manage the video A/D chip. The I2C interface pin functions are as follows:

IICSDA: I2C serial data terminal.

IICSCL: I2C serial clock output.

3.5 External HOST Interface Pin

The function of this interface pin is as follows:

MODE[1:0]: External HOST interface mode selection terminal? The specific selection methods are listed in Table 1. There are four modes to choose from. The system designed in this paper uses synchronous BURST mode 1.

Table 1 External HOST interface mode selection table

| Mode | MODE[1:0] | CPU |

| Synchronous BURST mode 0 | 00 | PLX9050/9080 |

| Synchronous BURST mode 1 | 01 | MPC850/860 |

| Synchronous BURST mode 2 | 10 | CYPRESS EZ-USB |

| Asynchronous SINGLE mode | 11 | INTEL MCU |

BW: External HOST interface bus width setting end. When connected low, HOST interface adapts to 16bits; when connected high, HOST interface adapts to 8bits width.

HD[15:0]: External HOST interface data bus.

HA[4:0]: External HOST interface address bus.

NCS: Chip select signal end of IME6400, low effective.

ADS: External HOST address strobe signal, active low.

NRD: External HOST data read strobe signal, active low.

NWR: External HOST data write strobe signal, low active.

FRD: The external HOST data quickly reads the strobe signal terminal and is active low.

USEOCK: Used to indicate the clock source used by the external HOST interface. When the pin is low, it means that the internal clock is used. When it is high, it means that the external clock is used.

HCLK: External HOST interface clock output.

NFULL: Bit stream FIFO status signal terminal. This pin outputs a high level when the FIFO is Half-full or Full.

READY: This pin can be used to indicate the data preparation status when the interface mode is synchronous.

3.6 Audio Codec Pins

The function of this interface pin is as follows:

CCLK: Audio codec clock signal input. The IME6400 supports audio samples at 32, 44.1, and 48 kHz. To support different sample rates, the input clock should be different. When CCLK is input to the 12.2880MHz clock, the system will support a sampling rate of 32kHz or 8kHz; when the CCLK input is 11.2896MHz, it will support a sampling frequency of 44.1kHz.

SDATA: Serial audio data line input.

SCLK: Serial audio clock signal output.

IRCK: Left-right clock signal output.

3.7 Other Pin Function Descriptions

CPUTEST: Internal CPU test terminal, high effective.

PLLTEST: Internal phase-locked loop test terminal, high efficiency.

FUNTEST: The chip function test terminal is highly effective.

DIV34: Clock mode select terminal for SDRAM. When connected low, it means that the clock frequency of SDRAM is 3 times of the main clock of the chip MCLK; when it is high, the clock frequency of SDRAM is 4 times of MCLK.

4 embedded monitoring system design

Through the research on IME6400, the author designed an embedded monitoring system, and Figure 1 is the design block diagram of the monitoring system. In the figure, after A/D sampling of audio and video signals respectively, the data will be input into IME6400 for MPEG4 compression encoding. The encoded compressed video stream is read by the embedded CPU through the HOST interface, and then can be stored to the hard disk or passed. The network is stored in other carriers.

4.1 Audio interface design

In this design, the audio A/D sampling uses TEXAS's PCM1801, which is a 5V powered dual channel ADC. The input clock is 11.2896MHz, which can accommodate 44.1Kbits sampling. The connection between PCM1801 and IME6400 is shown in Figure 2.

4.2 Video interface and I2C interface design

Video A/D uses ROCKWELL's BT829B. It can output digital video from the CCIR-601 interface. The BT829B has two sets of clock inputs. If you only use it to decode PAL video signals, you should input the clock to XT0I and take XT1I low. The BT829B can be used as an I2C slave device to connect to the I2C interface of the IME6400, so that the IME6400 can manage the BT829. The video interface connection mode is shown in Figure 3.

4.3 HOST interface design

The external HOST interface of the IME6400 is mainly used to transmit the encoded data stream. The mode of the four external HOST interfaces can be determined by the MODE pin. The mode selected for this design is synchronous Burst mode 1, corresponding to MODE?1:0? pin = 2' b 01. That is, it corresponds to the case of MPC850/860.

The embedded CPU can be selected from MOTORALA's MPC850. The HOST interface clock can be provided by MCLK or FRD, and its value can be determined by the value of USEOCK. In this design, since USEOCK is 1, FRD is used as the internal clock source. This 27MHz clock source can be provided by the main control board. The connection mode of the HOST interface is shown in Figure 4.

The MPC850 reads the compressed data from the HOST interface in Burst mode, and the IFULL signal of the IME6400 is directly input to the IRQ of the MPC850. Burst is programmable and is only used when reading compressed data. The maximum Burst length is 256 bytes, that is, 256 bytes can be read in one operation. This shows that the design can greatly improve the reading speed.

4.4 SDRAM interface design

In order to compress video and audio data and store the encoded stream, external SDRAM is generally required. Its size is related to the size and mode of the image to be compressed. The size of the SDRAM selected for this design is 2MB x 32. The IME6400 can access up to 2Gbits of external SDRAM. At present, the address size selected for this design is 11 rows and 8 columns.

The SDRAM clock is three times or four times the MCLK clock, which can be determined by the value of DIV34. In this design, the MCLK clock is 27MHz. When the MCLK clock is selected three times, the clock of the SDRAM is 27×3=81MHz. SDRAM uses K4643232E. The connection method is shown in Figure 5.

4.5 ROM interface design

If the internal boot ROM is used, the IME6400 does not require an external ROM, but in the external boot mode, a ROM interface is required. The external ROM can be up to 4MB. In this design, EXTBOOT uses jumper mode to control whether to use external or internal ROM to boot. The external ROM in this design uses 28C256, which is a 256kB (32KB × 8) and 5V powered storage device. The 27MHz clock of MCLK is provided by the main control board.

IME6400 has two ways to download FIRMWARE, which can be selected by the jumper switch on pin P236 (EXTBOOT). When the jumper switch is high, the external 28C256 is selected to start, and when it is low, it is selected to start from the MPC850.

5 Advantages of this monitoring system

The MPEG4 compression and embedded system designed with IME6400 hardware can greatly improve the performance of the monitoring system, mainly in:

(1) The video and preview are equally clear, the image format can achieve D1, and the full dynamic bit rate can be controlled at 200MB/hour.

(2) The compression speed is faster, and there is no lag delay in real-time streaming playback. The minimum delay can be less than 1 second.

(3) The compressed data can be read by Burst, which improves the reading speed and also creates conditions for the embedded CPU.

6 Conclusion

This paper provides an MPEG4 real-time audio and video compression technology solution by analyzing the IME6400 chip. An embedded MPEG4 video surveillance system is designed for commercial use.

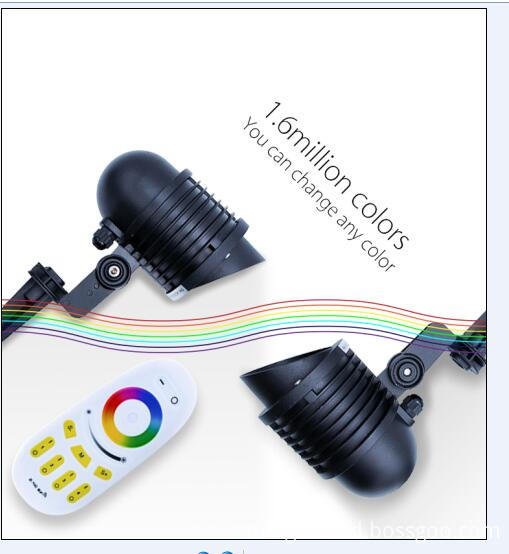

LED Garden Light is used for lawn around the lighting facilities, is also an important landscape facilities. With its unique design, the soft lights add to the safety of the urban green landscape

LED Garden light function: Beautiful, and easy to install, decorative and strong, can be used for parks, garden villas, pedestrian street, parking lot, square and other public places lawn green landscape area. Spacing between 6 to 10 meters is appropriate. There are some led garden light made of chic small animals or plants and other simulation modeling, placed in the lawn, as if the sculpture as beautiful.

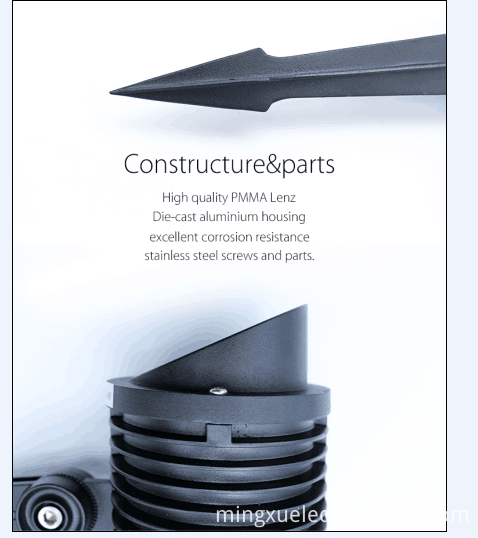

led garden light features:

1, high brightness: LED garden light selection of high-power LED, 5050 patch light source to provide adequate energy.

2, high quality: LED garden light selection of anti-corrosion, anti-aging aging of the manufacturing.

3, high life: can reach more than 100,000 hours.

4, energy efficient: LED garden lighting, energy saving.

5, high security: LED garden light is a low-voltage products, the use of DC 12V or 24V power supply, safe and harmless, for children, pedestrians and animals for effective protection. Light body with high strength structure design, wind, anti-external strength is high.

6, easy installation: easy installation, independent power supply, without erection or embedded transmission lines, construction is simple, low construction costs.

Outdoor LED Garden Light,LED Garden Light,Remote Control Garden Lights

Shenzhen Mingxue Optoelectronics CO.,Ltd , http://www.mingxueled.com